Issue

One Hundred Thirty

# Journal of Computer Resource Management

A Publication of The Computer Measurement Group, Inc.

The Computer Measurement Group, Inc. (CMG) is the most influential organization worldwide for the exchange of information among Computer Performance Evaluation (CPE) professionals. To keep CPE professionals on top of their field, CMG is dedicated to providing its members the education, networking, and leadership opportunities vital to success in today's competitive industry.

#### **PUBLICATIONS & MEMBERSHIP BENEFITS:**

- The *Proceedings* contain all the information presented at the annual CMG conference. With more than one hundred papers on current hot topics, the *Proceedings* is your best source of the latest information in the expanding field of CPE. Some Late Breaking papers may not be in the *Proceedings*; they appear in a *Journal* issue.

- The *Journal* provides an additional source of information with emphasis on special interest topics and/or focus on specific CPE industry issues. Members receive the *Journal* at least three times a year.

- The *Bulletin* is a newsletter written by members for members. This publication is available in electronic format and includes vital information on CMG's national, regional, and international groups.

- Various Internet Services. CMG provides various online membership only services including a directory of all CMG members.

- CMG's electronic newsletter, **MeasureIT**, sent to all those who subscribe.

#### **INFORMATION FOR AUTHORS**

The Journal of Computer Resource Management (CMG Journal) is distributed only to members of the Computer Measurement Group, Inc. (CMG). CMG membership consists primarily of practicing professionals in the area of computer performance, analysis, and capacity planning. The objective of the CMG Journal is to bring the membership information of current importance involving:

- performance characteristics of computer systems of all sizes and architectures

- techniques to measure, analyze, compare, predict, and report performance

- techniques for managing computer performance, including capacity management, computer cost accounting, and computer performance reporting

- integration of disparate components into hardware and software systems to meet organization needs.

The intent of CMG is to publish relevant papers as rapidly as possible, preferably within six months of completion. Authors can assist CMG in achieving this objective by submitting papers in a uniform format.

To submit your paper for consideration in the *CMG Journal*, it must follow a format consistent with CMG guidelines. For complete instructions on paper submittal you should download two documents from <u>http://www.cmg.org/national/journal.html</u> located on the CMG Website. These documents are 'Paper Guidelines and Instructions' and 'CMG License to Publish.' The first document will provide guidelines on format and text; the second document is a required form that must be signed/returned to CMG that grants your permission for CMG to publish your paper.

Here are some highlights on what is expected from authors:

- Camera-Ready Papers, in Microsoft Word, should be sent via email to journal@cmg.org

- Electronic copies of the paper are preferred; send two hardcopies of the paper in the required format (see 'Instructions' document for details) if an electronic copy is not possible. Hardcopies must be camera ready Papers should be submitted three months prior to the Journal publication date

- Please indicate if you wish to review the paper after editing, prior to publication

- Refer to all tables and figures by number

Authors must read and follow the 'Instructions for Preparing Papers' document. The above highlights do not include all the guidelines required for submitting your paper. Papers not complying with the instructions may be rejected for inclusion in the *CMG Journal*.

Entire publication copyright © 2011 by the Computer Measurement Group, Inc. All Rights Reserved. Front cover image: © Designer: Rob Harrigan | Agency: dreamstime.com

Published by the Computer Measurement Group, a not for profit Illinois membership corporation. Publication in the CMG Journal implies acknowledgment of the author's (or authors') copyright and republication rights. Permission to reprint in whole or in part may be granted for educational and scientific purposes upon written application to the Editor, the Computer Measurement Group, 151 Fries Mill Road, Executive Campus, Suite 104, Turnersville, NJ 08012. Permission is hereby granted to members of CMG to reproduce this publication in whole or in part solely for internal distributions within a member's organization provided the copyright notice printed above is set forth in full text on the title page of each item reproduced. CMG acknowledges the ownership of trademarks and registered trademarks that appear in this publication. They are each to be regarded as appearing with the appropriate @ or m symbols at first mention.

The ideas and concepts set forth in this publication are solely those of the respective authors, and not those of CMG. CMG does not endorse, guarantee, or otherwise certify any such ideas or concepts in any application or usage. Printed in the United States of America.

# Journal of Computer Resource Management

A Publication of the Computer Measurement Group

Issue 130

# Table of Contents

| Letter from the Editor                                                                 |

|----------------------------------------------------------------------------------------|

| Capacity Planning Concepts for Telecom Systems                                         |

| <ul> <li>Why Models Fail - A Case Study: A Workload Analysis Model</li></ul>           |

| <b>No</b> t Your Father's or Grandfather's Mainframe Anymore 26<br>David J. Lytle      |

| Processor Selection for Optimum Middleware Price/Performance                           |

| Exploratory Study of Performance Evaluation Models for DistributedSoftware Arhitecture |

S. O. Olabiyisi, E. O. Omidora, et al.

## CMG Journal #130: Letter from the Editor

Welcome to CMG Journal number 130, our third and final issue for 2011. Fall is upon us in the northern hemisphere, all the leaves are brown and the sky is gray. However, once again we have a great issue for you, guaranteed to brighten up your day and carry you through to Conference. This issue features six outstanding papers on a wide variety of topics. This will be our last issue for 2011.

Leading this issue off is Tim Sweetz with *Capacity Planning Concepts for Telecom Systems*. Telecom systems are the primary means of communication between customers and companies throughout the world. As these systems have evolved over time, the computerized infrastructure behind modern call centers provide companies with a high level of customization, but can also lead to complicated and expensive operational processes. One way to reduce costs associated with telecom technologies is through the discipline of capacity planning. Tim's paper will present some of the key concepts and basic methodologies required to provide capacity planning services for telecom systems.

Our second paper, *Why Models Fail-A Case Study: A Workload Analysis Model* is from frequent CMG contributor Tom Wilson. What does it mean for a model to fail? It means that the model failed to provide the insight that it was meant to provide. A model starts with an objective, has a design and implementation, and then is put to use. The case study in Tom's outstanding paper examines a workload analysis model, from which a performance test model is derived, and discusses why the model failed.

Our third paper, An Effective Implementation of CMMI for Performance Testing Projects – a Case Study was written by Nidhi Tiwari and Veena Rajendiran. Today performance testing is well recognized, widely practiced and sufficiently equipped with tools. However, little emphasis is given to process implementation, tracking and improvement of performance testing projects, resulting in exponentially high Cost of Quality (COQ). The authors share their experience implementing CMMI for performance testing projects to control their COQ. Subsequent benefits obtained by organization are also included in the paper.

Batting cleanup is David Lytle with his paper titled *Not Your Father's or Grandfather's Mainframe Any More.* David reviews the history of mainframe I/O and compares it with distributed systems I/O. He then highlights some of the more recent developments in mainframe I/O introduced the past three years and that are currently being implemented on the latest mainframe processors from IBM.

Our fifth paper, *Processor Selection for Optimum Middleware Price/Performance* was written by David Kra. Many middleware products can be deployed onto many combinations of processor architecture and operating system. Finding the most cost effective combination is complicated by software pricing based on vendor core weighting factors. David's paper explains how to combine core weights, core counts, and performance data to calculate and compare a "Performance Rate per Weighted Core." Results are provided for the Oracle data base server as used in published TPC-C and TPC-H benchmarks.

Last but not least is our sixth and final paper this issue. *Exploratory Study of Performance Evaluation Models for Distributed Software Architecture* was written by Boluwaji A. Akinnuwesi, Faith-Michael Uzoka, Hyacinthe Aboudja, Mathieu Kourouma, Victor W. Mbarika, S.O Olabiyisi, and E.O Omidiora. Several models have been developed to evaluate the performance of Distributed Software Architecture (DSA) in order to avoid problems that may arise during system implementation. This paper presents a review of DSA performance evaluation models with the view of identifying the common properties of the models. It was established in this study that the existing models evaluate DSA performance using machine parameters such as processor speed, buffer size, cache size, server response time, server execution time, bus and network bandwidth size and lots of others. The models are thus classified to be machine-centric. Moreover the involvement of end users in the evaluation process is not emphasized. Software is developed in order to satisfy specific requirements of the client organization (end-users) and therefore involving users in evaluating DSA performance should not be underestimated. This study suggests future works on establishing contextual organizational variables that can be used to evaluate DSA.

Thanks to everyone who contributed to this CMG Journal. CMG'11 is a month away and will be here before we know it. Hopefully you are planning on attending CMG'11, have registered, and if you have not already done so, please consider volunteering to help with the Conference. We are always looking for session chairs, and other on site volunteers to help at the Conference. Even if you are submitting a paper for the Conference, please consider writing a paper for the CMG Journal. You can submit your papers, as well as feedback to us at <u>cmgjournal@cmg.org</u>.

Thanks again for reading, and we hope you enjoy this issue.

Stephen R. Guendert, Ph.D

# CAPACITY PLANNING CONCEPTS FOR TELECOM SYSTEMS

Tim Sweetz Bank of America tim.sweetz@bankofamerica.com

Telecom systems are the primary means of communication between customers and companies throughout the world. As these systems have evolved over time, the computerized infrastructure behind modern call centers provide companies with a high level of customization, but can also lead to complicated and expensive operational processes. One way to reduce costs associated with telecom technologies is through the discipline of capacity planning. This paper will present some of the key concepts and basic methodologies required to provide capacity planning services for telecom systems.

#### Introduction

Arguably one of the most significant inventions in our history, the invention of the telephone in the late 1800s truly revolutionized communication methods. Replacing the well established telegraph infrastructure was not easy, but the technology of the telephone was a key enabler in the realm of communication that allowed for the sophistication and complexities that exist today. As the technology has continued to evolve over the years, the telephone is still a key component in telecom systems throughout the world.

Telecom systems provide the primary means of communication between customers and companies. While there are many aspects and technologies involved in telecom systems, the focus of this paper will be on Integrated Voice Response (IVR) systems. There are many benefits in having an efficient IVR system; for example:

- Automation of customer-based business processes

- Decreased call center staffing requirements

- Decreased time required to answer the customer's call

- Ability to provide self-service options to customer's without having to speak with a human agent

• Identify and authenticate the caller prior to human agent taking call to reduce call times

However, an inefficient or unavailable IVR system can have a very negative impact on a company's reputation. Like it or not, many customers associate the person on the phone with the company, and if the company will not answer their call, it is going to hurt the company's reputation. With this in mind, many companies rely on vendor recommendations and overprovision resources to ensure their IVR system will always be readily available. This is where the discipline of capacity planning, when applied appropriately, can be utilized to dramatically reduce costs and instill a sense of confidence that there will be enough capacity to accommodate peak periods in the call center.

#### **Telecom Capacity Planning**

Capacity Planning for IVR systems is not dramatically different than planning for many other types of systems; however, while many of the principles and methodologies involved in capacity planning for other systems remain the same, there are some significant differences that are typically only found when capacity planning for a call center environment. Specifically, the use of the Erlang Distribution is typically only used when planning for telecom technologies, although it is sometimes found in other cases as well.

#### **Erlang Distribution**

Capacity planning for telecom technologies utilizes a queuing theory based on the Erlang Distribution. The Erlang Distribution was developed in the early 1900s by Agner Krarup Erlang. While working for the Copenhagen Telephone Company in Denmark, Erlang developed mathematical formulae to evaluate the trade-off between low cost/poor service & high cost/excellent service. His work has been extremely influential across the globe and remains the basis for telecom engineering. In 1946, the International Consultative Committee on Telephones and Telegraphs (CCITT) adopted the name "erlang" as the basic unit of telephone traffic.

There are two main formulae for the Erlang Distribution: Erlang B and Erlang C. Erlang B, sometimes referred to as the Erlang Loss Formula, is the most commonly used formula and is designed to evaluate how many lines, or ports, are required for a specified amount of traffic. The other formula is the Erlang C, which allows one to calculate the probability that a customer will have to wait for a resource. In addition to these two main formulae, there is also the Extended Erlang B (sometimes referred to as Erlang B+), which is very similar to Erlang B but it assumes that a percentage of calls are immediately represented to the system if they encounter blocking.

#### Erlang

The basis for all Erlang calculations is the erlang. An erlang is a dimensionless unit of telecommunications traffic measurement describing the total traffic volume for a specified timeframe (typically one hour). Traffic in erlangs (E) is defined by the following formula:

$$E=\frac{\lambda h}{\mu}$$

- E = Total amount of traffic offered in erlangs

- $\lambda$  = Call arrival rate

- *h* = Average call handling time

- $\mu$  = Service Rate, or total time

For example, if you received 30 calls in one hour and each had an average duration of 5 minutes, the traffic figure would be (30 \* 5) / 60 = 2.5 erlang.

Finding the erlang number for your situation is rather straightforward and is the first step in using the Erlang formulas.

#### **Erlang B**

The Erlang B queuing model is denoted in Kendall notation as M/M/n/n. In this model, arriving customers have zero waiting positions. It assumes Poisson arrivals and exponentially distributed service times. Since the model does not provide for any waiting positions, if a customer finds no servers available, it is assumed the customer goes away and is lost. For this reason, the model is called a loss system. The lost customers are also said to experience blockage or to be blocked.

The Erlang B formula assumes an infinite population of sources, which jointly offer traffic to N servers. The rate of arrival of new calls is constant and does not depend on the number of active sources, because the total number of sources is assumed to be infinite. The rate of call departure is equal to the number of calls in progress divided by the mean call holding time. The formula was designed to calculate blocking probability in a loss system and provides the grade of service (GoS).

$$P_b = B(E,m) = \frac{\frac{E^m}{m!}}{\sum_{i=0}^m \frac{E^i}{i!}}$$

- $P_b$  = Probability of blocking

- *m* = number of resources (servers or circuits)

- *E* = Total amount of traffic offered in erlangs

#### Extended Erlang B

The Extended Erlang B, also referred to as Erlang B+, is an iterative calculation rather than a formula. It adds an extra parameter to the Erlang B formula, the recall factor, which defines the recall attempts. It assumes a specified number of calls are immediately represented to the system if they encounter blocking (a busy signal).

#### Erlang C

The Erlang C queuing model is denoted in Kendall notation as  $M/M/n/\infty$ , or simply M/M/n. As is the case with Erlang B, it assumes Poisson arrivals and exponentially distributed service times. However,

where the Erlang B model has zero waiting positions, the Erlang C model assumes an infinite number of waiting positions. Therefore, every arriving customer will eventually be served, even if they have to wait a long time. In direct contrast to the Erlang B model, no customer ever experiences However, if the number of erlangs blockage. exceeds the number of servers, then the system becomes unstable in the sense that the number of customers grows without limit. Part of the Erlang C queue definition specifies how waiting customers are serviced. It assumes a FIFO queuing discipline; the longest waiting customer will always be the next customer to begin service.

$$P_W = \frac{\frac{A^N}{N!} \frac{N}{N-A}}{\sum_{i=0}^{N-1} \frac{A^i}{i!} + \frac{A^N}{N!} \frac{N}{N-A}}$$

- *A* = Total traffic offerend in units of erlangs

- N = Number of servers

- $P_W =$

Probability that a customer has to wait for service

While one can certainly perform the calculations necessary to obtain the necessary output using the Erlang formulae, the process can become tedious. Because of this, the textbooks and tables that were previously required have been replaced by software with many Erlang calculators that are now widely available. Some are free to use and download, while others charge a nominal fee. There are also Excel plug-ins and code for C and JavaScript depending on your preferences. Any of these options make using the Erlang formulae quick and easy and are rather easy to find using your search engine of choice.

# Other Key Components for Telecom Capacity Planning

Now that we have detailed some of the basic concepts related to erlangs and the Erlang formulas, we need to briefly touch on the other key components involved in Telecom Capacity Planning: call volume and average handle time (AHT).

When dealing with call volumes, it is important to remember that calls have a tendency to bunch up. Because of this, all capacity planning efforts related to telecom traffic need to focus on peak periods. The industry norm is to deal with the peak hour. There are two primary options to choose from when attempting to determine the peak busy hour traffic. One method is to take the busiest hour from the past 13 months (if that amount of data is available) and use that as the peak. The other would be to take the busiest hour of each day for five or ten days during the busiest time of the year, and then calculate the average of those hours' traffic load to derive the average busy hour. This decision can be driven by business requirements, but in my experience it is best to go with the actual peak hour. Averaging peak values just has the potential to water down the peak to a point that can leave you susceptible to unavailability during a true peak period.

The other key input that we need for telecom capacity planning is the AHT. Simply stated, AHT is a telecom metric for the average duration of one transaction. AHT is typically measured from the caller's initiation of the call and including any hold time, talk time, and related tasks. AHT is required to determine the number of erlangs which is a key input into the Erlang formulae.

#### Putting it all together

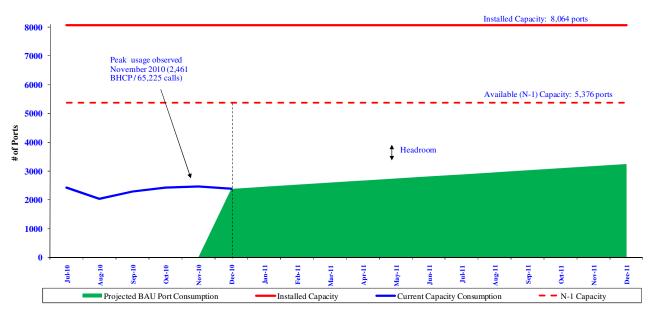

Now that we have an understanding of these key concepts, we will bring it all together with some hypothetical examples. Using a typical telecom environment, we have IVR servers located in three data centers. Each data center has 14 servers, and each server has 192 physical ports available. Accounting for disaster recovery, our SLA states we must be able to handle the peak workload across any two data centers at any time (N-1). We have accumulated call volume data for the previous 6 months, and we have obtained the peak hourly call volume and the AHT. In addition, we have compiled the busy hour concurrent port (BHCP) usage at the server level. In the absence of specific call volume projections, the business is providing a BAU growth projection of 3% per month. This information is summarized below and can be used to build a simple linear capacity model to visually represent the capacity forecast for the next 12 months.

| BHCP | Peak Call Volume                                                           | AHT                                                                                                                                                                                                                                                             | Erlang                                                                                                                                                                                                                                                                                   |

|------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2434 | 62,450 / hour                                                              | 132 seconds                                                                                                                                                                                                                                                     | 2290                                                                                                                                                                                                                                                                                     |

| 2048 | 52,231 / hour                                                              | 132 seconds                                                                                                                                                                                                                                                     | 1915                                                                                                                                                                                                                                                                                     |

| 2282 | 58,876 / hour                                                              | 131 seconds                                                                                                                                                                                                                                                     | 2142                                                                                                                                                                                                                                                                                     |

| 2420 | 61,175 / hour                                                              | 134 seconds                                                                                                                                                                                                                                                     | 2277                                                                                                                                                                                                                                                                                     |

| 2461 | 65,225 / hour                                                              | 134 seconds                                                                                                                                                                                                                                                     | 2316                                                                                                                                                                                                                                                                                     |

| 2384 | 60,673 / hour                                                              | 133 seconds                                                                                                                                                                                                                                                     | 2242                                                                                                                                                                                                                                                                                     |

| 2338 | 59,605 / hour                                                              | 133 seconds                                                                                                                                                                                                                                                     | 2197                                                                                                                                                                                                                                                                                     |

| 2461 | 65,225 / hour                                                              | 134 seconds                                                                                                                                                                                                                                                     | 2316                                                                                                                                                                                                                                                                                     |

|      | 2434<br>2048<br>2282<br>2420<br>2461<br>2384<br><b>2338</b><br><b>2461</b> | 2434       62,450 / hour         2048       52,231 / hour         2282       58,876 / hour         2420       61,175 / hour         2461       65,225 / hour         2384       60,673 / hour         2338       59,605 / hour         2461       65,225 / hour | 243462,450 / hour132 seconds204852,231 / hour132 seconds228258,876 / hour131 seconds242061,175 / hour134 seconds246165,225 / hour134 seconds238460,673 / hour133 seconds238559,605 / hour133 seconds246165,225 / hour134 seconds238659,605 / hour133 seconds246165,225 / hour134 seconds |

Table 1 – Historical Call Data

| Site          | # of Servers | Total # of Ports |

|---------------|--------------|------------------|

| Data Center 1 | 14           | 2688             |

| Data Center 2 | 14           | 2688             |

| Data Center 3 | 14           | 2688             |

| TOTAL         | 42           | 8064             |

| TOTAL (N-1)   | 28           | 5376             |

Table 2 – Infrastructure Data Used in Example

# **Company XYZ IVR Capacity Forecast**

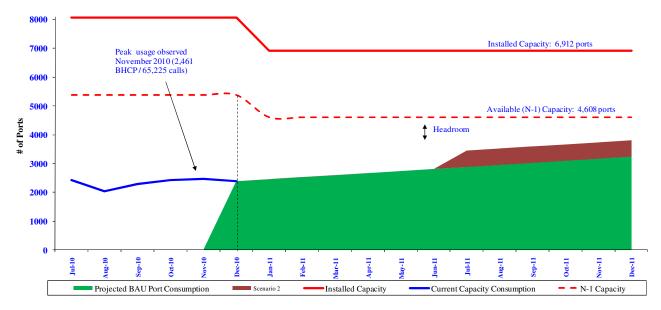

Figure 1 – Example Capacity Forecast Chart

As seen in Figure 1, the company has been underutilizing the available hardware and ports. Over the past six months, the peak port usage is 46% of their N-1 capacity threshold of 5,376 ports. However, given the aggressive growth projection of 3% per month, the forecast by the end of the year is 3,242 ports, or 60% of their N-1 capacity. Given this

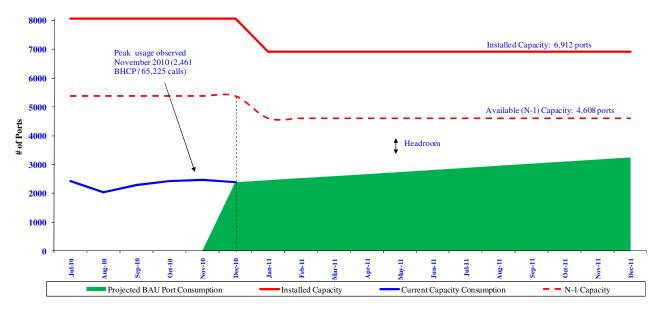

level of utilization, there would be an opportunity to cut costs by reducing the number of servers and ports in their environment. The following graph shows what the company's IVR system's capacity would look like if we released two servers from each data center (6 total servers):

Figure 2 - Capacity Forecast Chart Showing Reduction in Capacity

As seen in Figure 2, even after removing these 6 servers from the environment, the company would maintain sufficient capacity through the end of the year. Given the forecast of 3,242 ports in December 2011, the company would be using 70% of their N-1 capacity while still maintaining a nice buffer of 30%. Releasing 6 servers and 1,152 ports would present a significant cost savings while still maintaining a high level of service and confidence in the capacity of the environment.

### **Practical Examples**

Another key application of these telecom capacity concepts involves analyzing changes in either call volume or AHT, typically associated with a project or marketing campaign. Several scenarios are presented below:

- A new marketing campaign slated for May 2011 in which the business anticipates a 20% increase in call volume and no change in AHT

- A significant change in product slated for July 2011 in which the business anticipates a 10% increase in call volume and an increase in AHT by 10 seconds

- A code release expected to improve efficiency of the IVR system slated for September 2011 in which the business anticipates no change in call volume but a decrease in AHT by 15 seconds

### Scenario 1

For the first scenario, in which we anticipate a 20% increase in call volume and no change in AHT, we would utilize the Erlang B formula to determine the number of ports required for this increased workload. The steps are detailed next:

- Use the peak hour call volume (65,225) to calculate the new peak with the additional 20%: 65,225 \* 1.2 = 78,270

- Find the number of Erlangs for the increased call volume (using same AHT of 134): (78270 \* 134)/3600 = 2913 erlangs

- Next, find the number of ports required to support this increased workload (using an Erlang B calculator): 3,073 ports required

- Find the difference between the new projected peak and the current actual peak: 3073 2461 = 612 ports

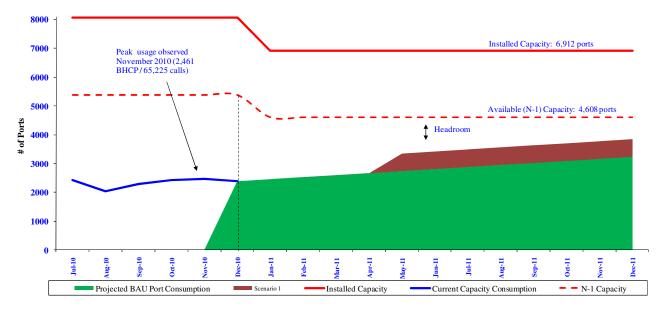

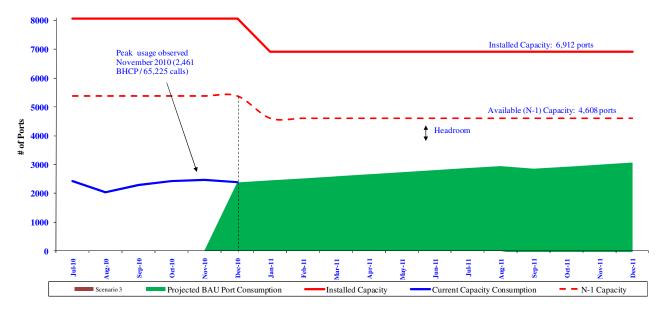

Given the projections in this scenario, the IVR system would need an additional 612 ports to support the marketing campaign. We can plug this number back into our capacity forecast model to determine if this will push us over our thresholds or if we will have sufficient capacity to accommodate this additional volume. As seen in Figure 3, the increase in call volume would obviously increase our usage, but we would still be well within our capacity thresholds.

Figure 3 – Capacity Forecast Chart Showing Impact from Scenario 1

### Scenario 2

For the second scenario, in which we anticipate a 10% increase in call volume and a 10 second increase in AHT, we would also utilize the Erlang B formula to determine the number of ports required for this increased workload. The steps are detailed next:

- Use the peak hour call volume (65,225) to calculate the new peak with the additional 10%: 65,225 \* 1.1 = 71,748

- Find the number of Erlangs given the increase in call volume and AHT: (71748 \* 144)/3600 = 2870 erlangs

- Next, find the number of ports required to support this increased workload (using an Erlang B calculator): 3,029 ports required

- Find the difference between the new projected peak and the current actual peak: 3029 - 2461 = 568 ports

Given the projections in this scenario, the IVR system would need an additional 568 ports to support the expected workload changes due to the change in product. We can then plug this number back into our capacity forecast model to determine if this will push us over our thresholds or if we will have sufficient capacity to accommodate this additional volume. As seen in Figure 4, the increase in call volume would increase our usage, but we would still be well within our capacity thresholds.

Figure 4 – Capacity Forecast Chart Showing Impact from Scenario 2

Finally, for the final scenario in which we anticipate no change in call volume but a 15 second decrease in AHT, we would also utilize the Erlang B formula to determine the number of ports required for this decreased workload. The steps are detailed next:

- 1) Use the existing peak hour call volume: 65,225

- Find the # of Erlangs given the decrease in AHT: (65225 \* 119)/3600 = 2156 erlangs

- Next, find the number of ports based on this decreased workload (using an Erlang B calculator): 2,296 ports required

4) Find the difference between the new projected peak and the current actual peak: 2296 - 2461 = -165 ports

Given the projections in this scenario, the IVR system would see a decrease of 165 ports as a result of the expected decrease in AHT due to the efficiencies gained from the code changes. We can then plug this number back into our capacity forecast model to adjust our forecast accordingly. As seen in Figure 5, the impact is not as significant as the first two scenarios, but the decrease is observed.

Figure 5 – Capacity Forecast Chart Showing Impact from Scenario 3

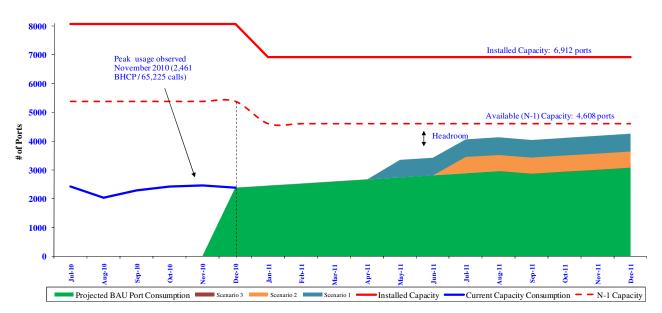

### **Combining the Scenarios**

The real benefit to modeling impact from various scenarios is when multiple changes are planned and you need to determine what your capacity will look

like when they are all combined. This holistic view is critical to ensuring you provide a telecom environment that has adequate capacity. The three scenarios are now shown together in Figure 6.

# **Company XYZ IVR Capacity Forecast**

Figure 6 – Capacity Forecast Chart Showing Impact from all Three Scenarios

As seen in Figure 6, the impacts from all three scenarios combined bring us closer to our N-1 threshold, but we still forecast sufficient capacity. The third scenario, while not looking as significant by itself, really helps bring the forecast down when taking all three scenarios into account. Without the decrease gained from scenario 3, we would be right at our N-1 threshold and most likely looking at adding capacity to provide more breathing room.

#### Conclusion

Capacity planning for telecom systems involves some unique concepts not found in other disciplines of capacity planning. In order to provide capacity planning services for telecom systems, one should work to develop an understanding of these concepts. This paper has provided an overview of erlangs and the Erlang formulas, as well as discussing some other key inputs involved in telecom capacity such as call volume and average handle time. With an understanding of these concepts, the remaining steps to develop a telecom capacity plan follow standard capacity planning methodologies. Collecting good data in terms of your call volumes and average handle times will be critical in developing a quality capacity plan for your telecom systems.

#### References

[ABST08] "About Queuing Models" <u>Abstract Micro</u> June 2, 2011:

<<u>http://abstractmicro.com/erlang/helppages/mod-about.htm#kendall</u>>.

[ABST08] "Erlang B Queuing Model" <u>Abstract Micro</u> June 2, 2011:

<<u>http://abstractmicro.com/erlang/helppages/mod-b.htm</u>>.

[ABST08] "Erlang C Queuing Model" <u>Abstract Micro</u> June 2, 2011:

<<u>http://abstractmicro.com/erlang/helppages/mod-</u> <u>c.htm</u>>.

[ANGU01] Angus, Ian, "An Introduction to Erlang B and Erlang C," Telemanagement #187 (July-August 2001).

[EVEN11] "Resource Dimensioning Using Erlang-B and Erlang-C," <u>Event Helix</u> June 6, 2011: http://www.eventhelix.com/RealtimeMantra/Congesti onControl/resource dimensioning erlang b c.htm>.

[SHAM09] "Using the Erlang Equation" <u>Shamrock</u> <u>Software</u> June 6, 2011: <<u>http://www.shamrock-</u> <u>software.eu/erlang.htm</u>>.

[WEST11] "What is an Erlang," <u>Westbay Engineers</u> <u>Limited</u> June 3, 2011: <<u>http://www.erlang.com/whatis.html</u>>.

# Why Models Fail—A Case Study: A Workload Analysis Model

#### Tom Wilson

What does it mean for a model to fail? It means that the model failed to provide the insight that it was meant to provide. A model starts with an objective, has a design and implementation, and then is put to use. This case study examines a workload analysis model, from which a performance test model is derived, and discusses why the model failed.

# 1 Introduction

Models come in various forms, but their common purpose is to increase our understanding of the things being modeled. Models give us the ability to be proactive concerning problems. Models are not necessary since we can move forward in ignorance and react to problems as they are encountered. As silly as this perspective sounds, it is too common. However, what may be worse than doing nothing is creating an ineffective model.

So, what does it mean for a model to fail? It means that the model failed to provide the insight that it was meant to provide. This probably means that there was something wrong with the design, implementation, or use of the model (we will assume that at least we got the objective right). A model's design incorporates its goal or intent. This is sometimes where the design will go wrong. The implementation concerns the details of how the model accomplishes its goal. Errors in the model can render it useless. A model's use includes the data put into the model. Bad inputs result in bad outputs. This is common point of failure for a complex model.

This paper will describe a real model and then discuss where it fell short of its objective. The sections containing the model's details may be skimmed (Sections 2 and 5) or skipped (Sections 3 and 4) and later referenced after reading the conclusions (Section 6).

# 2 Model Objective

An existing proprietary transaction system supports logistics and maintenance of military equipment. A new system is being designed to provide more functionality and storage and serve a larger user base. A *Service Level Agreement* (SLA) will be used during operations to determine payments to the contractor by the customer. The existing system also has an SLA governing operations, although it differs from the new system's SLA in a few unimportant aspects.

A performance test model will be used to evaluate the new system against the SLA since the SLA is the only guidance for developing the system. The performance testing will help management assess the performance risks associated with the new system before it enters into production. The performance test model requires a workload upon which to base its assessment. So, it is important that the performance test model have an accurate workload. A performance test model should account for:

- the frequency of the functionality in the workload

- the timing of the workload

- the data being operated on by the workload

The frequency of the functionality specifies which functionality is executed and how often. Note that not all functionality needs to be executed in a performance test. The timing of the workload directly impacts the load on the system. In an interactive system, think times separate the activities performed by the users. Think times dictate throughput and are not accounted for in this workload analysis. [Wil10a] describes think times and other user analyses.

Determining the data being operated on is a complex analysis. That analysis is influenced by roles that the user can take on as well as privileges that he has. Some users have access to more data than other users, but that does not mean that such users access all of the data that they can. This aspect of the workload model was not addressed by the WAM since there was no simple way to mine such data from the existing system. [Wil11a] describes some of the issues concerning workload data.

Functionality is described by means of a *Business Process* (BP). A BP details the actions that the user takes when using the system. Here, a BP is synonymous with an engineering use case. A BP can have many paths of execution based on choices and/or parameter settings, such as permissions. The *Workload Analysis Model* (WAM) defines the BP workload for the performance test model. What the WAM needs to produce is a list of frequencies for the BPs.

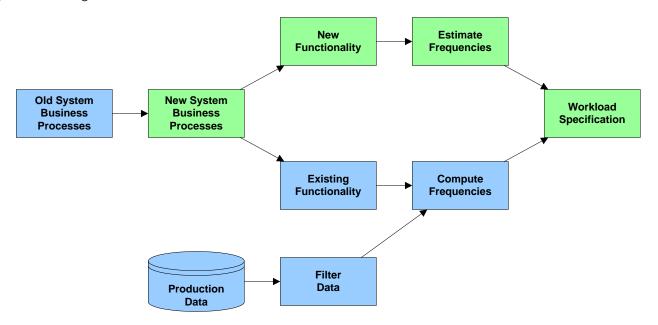

# 3 Model Design

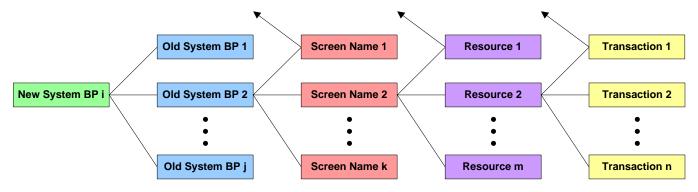

Conceptually, the WAM design is fairly simple. The new BPs are divided into groups of new and existing functionality. Existing functionality is determined by an association with a BP in the existing system (termed "old BPs"). Frequencies for old BPs are determined by analysis of production data. Frequencies for new BPs with new functionality are estimated based on comparison with new BPs with existing functionality. The two groups are then combined to produce the workload specification. Figure 1 illustrates the WAM.

**Figure 1:** This figure illustrates how the WAM is constructed. The green boxes indicate tasks involving new functionality, while blue boxes indicate tasks involving existing functionality.

In practice, several of these steps are difficult. We want BP frequencies for the new system but only have transaction data from the existing system. Transactions are associated with a *resource*<sup>1</sup> within the software. This association turns out to be many-to-many. The resources are associated with *screens*. This association is also many-to-many. Finally, screens are associated with the BPs; again, this is a many-to-many association. Figure 2 illustrates the mapping concept. This mapping allows us to produce frequencies for the new system BPs as long as it has corresponding old system BPs.

Since the old system is complete, one would think that all of the desired information would be available. Unfortunately, this is not true. Most of the relationships are not documented and were derived by design and development *Subject Matter Experts* (SMEs).

# 4 Model Implementation

The WAM is implemented as an Excel spreadsheet, which is a collection of worksheets. The implementation is presented by describing the worksheets. One worksheet contains the few user-specified parameters that there are to the WAM. One specifies the number of users in the performance model. This parameter determines the number of each script that should

<sup>&</sup>lt;sup>1</sup>Unfortunately, I cannot find an adequate description for this term.

Figure 2: This figure illustrates the difficult task of mapping transactions to the business processes of each system.

be run. Another parameter determines the percentage of old functionality in the new system. This is used on the BP summary worksheet (described in Section 4.4). The remaining worksheets are described in the subsequent subsections.

#### 4.1 Production Data Worksheet

The production data worksheet contains pairs of resources and transactions and their counts obtained by mining production data. A filtering process is applied to the data so as to eliminate transactions that do not contribute to the computation of BP frequencies. Figure 3 shows the filtering process.

Figure 3: This figure illustrates the transaction filtering process.

The first filtering operation removes all data that do not fall within the interval of interest. The interval of interest is defined as the time periods where high user-counts (called "peak-transaction-hour data") exist. We will not bother detailing the periods any further because other analysis shows that the frequency of functionality is roughly the same across all time periods (refer to [Wil10b]). Nonetheless, transactions outside the high-user-count time periods were discarded.

Two filtering operations are applied to the peak transaction hour data in order to eliminate some anomalies that inflate the activity frequencies. The first concerns overlapping or nearly overlapping transactions. If an activity outputs more than one transaction, we do not want to count all the transactions toward the frequency of the activity. There are other times that multiple transactions can be output. In the case of a slow response, the user may submit the transaction again. This is not normal behavior and should not influence the frequency of the activity. There can also be occasions where two transactions do not overlap, but are so close together that they are not likely to be different actions by the user. A one-second threshold was used to define transactions that are nearly overlapping.

For the remaining data, other transactions are removed if they are considered not to be indicative of the functionality. Examples include navigational transactions and error-related transactions. In the former case, a user may move from one screen to another. In the production data, the transaction generated is associated with the screen being left. This is not a true usage of the screen's functionality. In the latter case, transactions can be generated that give error messages back to the user. This is not representative of what the user is trying to accomplish.

A list of transactions is the output of the mining and filtering process. Over 1 million transactions remained after the filtering process. Associated with each transaction is a resource. The production data worksheet has pairs of resources and transactions with associated counts.

#### 4.2 Resource Frequency Worksheet

The resource frequency worksheet allows a resource remapping to occur before the final frequency is computed from the production data. In a small number of cases, a resource and its group of transactions were not indicative of the activity on a screen. A mapping step allows a resource to be given an alternate name and assigned a subset of its transactions. Only a small number of resources required this mapping. All others were mapped to the same resource name. Table 1 shows an excerpt of the worksheet.

| Resource |       |                   |        |       |

|----------|-------|-------------------|--------|-------|

| Alt.     | Orig. | Transactions      | Count  | Freq. |

| 2        | 2     | 105               | 873    | 0.08% |

| 3        | 3     | 105, 110          | 54,023 | 4.88% |

| 4        | 4     | 105               | 331    | 0.03% |

| 6        | 6     | 105               | 10     | 0.00% |

| 7        | 7     | 3                 | 499    | 0.05% |

| 8        | 8     | 5, 92, 94-96, 105 | 1,059  | 0.10% |

| 9a       | 9     | 132               | 0      | 0.00% |

| 9b       | 9     | 142               | 0      | 0.00% |

| 9c       | 9     | 105, 120, 140     | 1,402  | 0.13% |

Table 1: Resource/Transaction Counts and Frequencies (Excerpt)

Resource 9 has 5 transactions associated with it. Two of these transactions indicated different functionality than the other three. In this particular case, the count for each of those transactions is 0. This is because the transactions occurred in production, but during time periods which were filtered out. So, why bother splitting the resource? Because the transactions occurred with other resources which were also split. So, some transactions caused resources to be split regardless of the counts for the transactions.

The list of alternate resources has a list of transactions associated with it. From these transactions, a frequency can be computed for the resource. These resources and frequencies are then used on the BP mapping worksheet (discussed in Section 4.3). There were originally 118 named resources and 165 named transactions. After splitting resources, there were 131.

#### 4.3 BP Mapping Worksheet

The BP mapping worksheet consists of a list of new system BPs with zero or more old system BPs mapped to it. Each old system BP has a list of zero or more screen names associated with it. The reason why there could be zero screen names is because these lists were reverse engineered from the production data. The complete list of old BPs was created from engineering documentation; the lists of screen names were derived from the reverse mappings of transactions and resources (which occurred during operations) to screens. So, if a screen was never visited, it does not appear.

Table 2 shows an excerpt of the worksheet that captures these mappings. Because of the many-to-many mappings, a resource, a screen, or old BP can occur several times. Examples are resource 49, screen 45, and BP 06.15. This makes numerous rows in the worksheet. The resource frequencies, which are computed on the resource frequency worksheet, and are evenly distributed across all occurrences (introducing error since the distribution is probably not uniform). For example, resource 49 occurs two times in the actual spreadsheet. Its frequency of 2.32% is distributed evenly across the associated screens. The frequency of any new BP is simply the sum of all of the relevant rows.

| New System |       | Old System |        |      |       |

|------------|-------|------------|--------|------|-------|

| BP         | Freq. | BP         | Screen | Res. | Freq. |

| 001.1.a    | 3.00% | 06.01      | 45     | 49   | 1.16% |

|            |       | 06.02      | 45     | 49   | 1.16% |

|            |       | 06.07      | 45     | -    | 0.00% |

|            |       | 06.15      | 46     | 50   | 0.33% |

|            |       | 06.16      | 46     | 50   | 0.33% |

|            |       |            | 74     | 88   | 0.02% |

| 001.1.b    | 0.78% | 06.03      | 07     | 08   | 0.03% |

|            |       | 06.04      | 07     | 08   | 0.03% |

|            |       | 06.05      | 07     | 08   | 0.03% |

|            |       |            | 68     | 85   | 0.01% |

|            |       | 06.08      | 07     | -    | 0.00% |

|            |       | 06.15      | 46     | 50   | 0.33% |

|            |       | 06.16      | 46     | 50   | 0.33% |

|            |       |            | 74     | 88   | 0.02% |

Table 2: Business Process Frequencies Mapping (Excerpt)

### 4.4 BP Summary Worksheet

The BP summary worksheet lists all BPs and computes their final frequencies. Table 3 shows an excerpt of the worksheet. Each BP is defined as *new*, *old*, or *both* (only one BP is marked as *both*). For those marked as *old*, frequencies come from the BP mapping worksheet. New frequencies are estimated and are manually entered on this worksheet.

|         | Func. | Comb. | New   | Old   |

|---------|-------|-------|-------|-------|

| BP      | Туре  | Freq. | Freq. | Freq. |

| 001.1.a | Old   | 1.20% | 0.00% | 3.00% |

| 001.1.b | Old   | 0.31% | 0.00% | 0.78% |

| 001.1.c | Old   | 0.00% | 0.00% | 0.00% |

| 001.1.d | Old   | 0.32% | 0.00% | 0.79% |

| 001.1.e | New   | 0.06% | 0.10% | 0.00% |

| 001.1.f | Old   | 0.27% | 0.00% | 0.68% |

| 001.2.a | New   | 0.94% | 1.56% | 0.00% |

| 001.2.b | Old   | 2.78% | 0.00% | 6.95% |

| 001.2.c | New   | 0.44% | 0.73% | 0.00% |

| 001.2.d | Old   | 0.05% | 0.00% | 0.11% |

| 001.2.e | New   | 0.44% | 0.73% | 0.00% |

Table 3: Final New System BP Frequencies (Excerpt)

A manual process was used to estimate the frequencies of the new functionality. First, all of the BPs with existing functionality were assigned to groups with the following frequency ranges: 0%, 0-1%, 1-5%, 5-10%, 10-15%, and  $\geq$ 15%. Then a SME that was knowledgeable in both systems assigned BPs with new functionality to the groups based upon similarity to the BPs already present in the range.

Initially, the frequency for each BP with new functionality was assigned the midpoint value of its range (no BP was assigned to the " $\geq 15$ %" range). The resulting values were then normalized. These final values are manually entered on this worksheet.

Finally, the new and existing functionality are combined by scaling their associated frequencies. The same SME provided a guess as to the frequencies of new and old functionality. That guess was 60% and 40%. So, the combined frequencies are the result of scaling the new and old frequencies by the appropriate value.

### 5 Model Usage

Using the model requires it to be populated with data. Most of the data came from mining production data. Relationships between transaction, screens, and BPs came from source code and SME knowledge. These take the form of data in the spreadsheet. Other data came from SME estimates. Finally, the number of users is entered, and the spreadsheet computes the number of each BP to have in the workload.

When scripts were being recorded, it was realized that many BPs (e.g., searching for equipment) were necessary to execute other BPs. The WAM was computing the frequency of BPs but not the frequency of the scripts (the fact that scripts were named after BPs was a point of confusion).

In an attempt to correct this, a new worksheet was added that captured what BPs occurred in each script so that the frequencies of the scripts could be adjusted to improve the frequencies of the BPs. The population of the worksheet was not supported due to schedule pressures and the WAM's BP frequencies were used for the script frequencies. The result was an inaccurate workload.

## 6 Conclusions

The problem with the WAM was that it was outputting BP frequencies rather than script frequencies. In some cases, a script and BP were equivalent. However, in many cases, a script contained two or more BPs. Some BPs occurred in several scripts. In the end, frequencies for the BPs in the collection of scripts did not match the WAM frequencies.

The WAM could have been less complicated. First, some concept of scripts needed to be defined in the old system. This would mean identifying sequences of BPs that would make up those scripts. Such scripts would need a counterpart in the new system. Then frequencies for the old system scripts would be derived from transaction information. Additional

scripts would be defined for new functionality with associated frequencies. The result would be a more accurate workload. The biggest challenge would be computing the frequencies for the old system scripts based upon sequences of BPs.

Also, not all functionality needed to be considered for a performance test. This would not only remove some of the data that was mined, but also reduce the number of scripts that had to be developed and maintained (because the software was still be developed).

This modeled failed because of misalignment of the types of workload. Transaction workload was gathered from the existing system, yet BPs were modeled in the performance test. The model also attempted to cover too much functionality and had too low a level of detail.

# 7 Series Summary

This series provided examples of why models can fail to achieve their goals. In [Wil11c], the model lacked data. No input means no output. No output means that the model has no use in spite of its detail and potential. The source of most of the needed data was the customer. Gathering these data was not a priority in the project.

In [Wil11b], lack of data was also an issue. However, in this case data were needed from both the customer and the contractor. For the contractor, most of the missing data was related to incompleteness of the design or the absence of tests to gather measurements. Again, gathering these data was not a priority in the project.

In this paper, the design was flawed. Most aspects of the model's design and implementation are correct, but the misalignment of the types of workload results in bad data in the model. Unfortunately, no analysis was performed to compare the performance test's workload with the actual production workload after the system was deployed.

Finally, we will say that we should probably not judge the models using a pass-fail assessment. No model is perfect, so we must allow some amount of error. However, even that perspective is very subjective. In all cases, the various phases of the model development allowed things to be learned about the system under development. But, if that alone were the goal, the effort could be better focused. Nonetheless, the models could have been much more useful.

# References

[Wil10a] Tom Wilson. "Data Mining User Behavior". CMG MeasurelT, September 2010.

- [Wil10b] Tom Wilson. "Workload Correlation and Visualization". *Proceedings of the CMG 2010 International Conference*, December 2010. Reprinted in *CMG MeasureIT*, Issue 5, 2011.

- [Wil11a] Tom Wilson. "Developing Toward an SLA: Understanding Data Complexity". CMG MeasureIT, Issue 3, 2011.

- [Wil11b] Tom Wilson. "Why Models Fail-A Case Study: A Multi-year OLTP and OLAP Database Storage Capacity Model". Journal of Computer Resource Management, Issue 129:13–19, 2011.

- [Wil11c] Tom Wilson. "Why Models Fail–A Case Study: A Transaction Synchronization Model for Computing Removable Media Capacity". *Journal of Computer Resource Management*, Issue 128:18–29, Winter 2011.

# An Effective Implementation of CMMI for Performance Testing Projects – a Case Study

Nidhi Tiwari, Infosys Technologies Ltd., nidhi\_tiwari@infosys.com Veena Rajendiran, veena.rajendiran@gmail.com

Today performance testing is well recognized, widely practiced and sufficiently equipped with tools. However, little emphasis is given to process implementation, tracking and improvement of performance testing projects, resulting in exponentially high Cost of Quality (COQ). Here we share our experience of implementing CMMI for performance testing projects to control their COQ. Subsequent benefits obtained by organizations are also included.

### Introduction

Today performance of software systems in terms of throughput, responsiveness etc is becoming critical for various businesses. Its awareness has in turn boosted the performance testing technology [1]. Consequently, a plethora of integrated suites of products like Mercury's LoadRunner, Radview WebLoad etc are available to verify the performance of business-critical applications. However, it is observed that performance testing projects run over schedule and budget, with much chaos and ambiguity. A key reason for this is a lack of identification and conformation to well-defined processes for performance testing.

Ad-hoc execution of projects results in schedule and budget slippages. Their people centric execution makes their success dependent on individual's skill level and experience. Defining a work process for performance testing would allow streamlining the activities and make them person independent to some extent. Further implementation of the Capability Maturity Model Integration (CMMI) framework would instill continuous process improvement and help sustain the quality of products i.e. system performance [2].

In this paper we use a case study to highlight some of the practical issues experienced during performance testing projects in the absence of any formal process. We illustrate a process and CMMI framework implementation for this organization and show the COQ improvement through various levels.

The paper is structured as follows: Section 1 sets context of the case study used in this paper, section 2 provides a brief overview of CMMI framework, section 3 describes implementation of CMMI for performance testing projects, and section 4 lists the benefits achieved by using CMMI and section 5 presents summary and conclusion for the paper.

#### A manufacturing client was facing numerous issues in performance testing projects such as frequent schedule slippages, errors slippages to production etc. Due to these issues, their downtimes and rework costs of code and testing were increasing, so they wanted to minimize performance related issues and risks in production while meeting tight delivery timelines. The client engaged us to provide high quality and efficient performance testing.

To understand the client performance testing methodology, brain storming sessions were done with the client team, available documents / reports were studied and joint tests were conducted. Subsequently, the following root causes were identified for their aforementioned problems:

- Lack of common definition and/or understanding of performance testing terminologies in the organization.

- Lack of standard process, templates and checklists available for performance testing.

- Unavailability of estimation models for performance testing

- Lack of a knowledge sharing process in place.

- Lack of a validity process for COTS acquisition

- Dependency of performance tests on individual's experiences.

After analysis and discussion, it was decided that the client's ad-hoc performance testing mechanisms need to be streamlined using a comprehensive and progressing framework. For doing so a work group of subject matter experts (SMEs) was formalized consisting of people from the performance engineering research group, performance testing practitioners group and process consultants. This group decided on using the CMMI framework based on dynamics involved in performance testing. Here we describe the progress of client processes through various CMMI maturity levels.

### 2. CMMI overview

CMM Integration (CMMI) model provides a set of guidelines for evaluating and improving an organization's

### 1. Case Study

software development processes [3]. As it has successfully helped a large number of IT organizations in streamlining their software development activities, CMMI guidelines were adopted to improve the performance testing process.

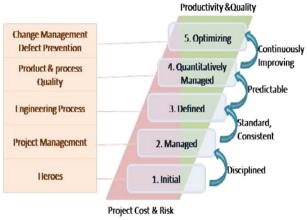

As shown in Figure 1, the CMMI® model is a method for organizing evolutionary steps into five levels of maturity that lay successive foundations to support process improvement. Processes at level 1 are very unpredictable and have great variability, while those at level 5 are highly predictable and continuous.

Figure 1: The SEI CMMI framework

As CMMI is a non-prescriptive model, we have extended it suitably for performance testing projects. We describe our experience of mapping CMMI practices to performance testing.

# 3. CMMI implementation for Performance Testing projects

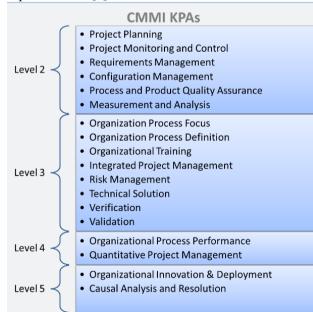

For performance testing projects following Key Process Areas (KPAs) at various levels were identified for CMMI implementation [4]:

Figure 2: KPAs for CMMI model

# 4.1. Level 1

Initially the cost and schedule were a high priority for the project manager. So the performance testing team's job was completely directed to report the test results quickly. There was no clarity about objectives, success criteria, process etc for test execution. Test scripts were recorded and executed in an ad-hoc manner as requests came in from the client for different applications/transactions. There was a lot of dependency on COTS (Commercial Off-Shelf Tools, i.e. third party tools like Webload, LoadRunner etc) for reporting, without any focus on building expertise in the field. These COTS were often used without much diligent background work, based on their cost and availability.

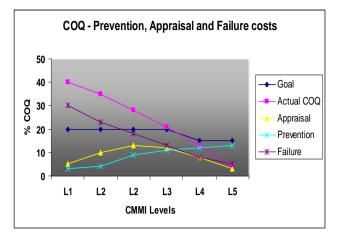

Though cost was given highest priority, no measures other than these quick fixes were adopted. Estimation was not based on any formal process. Project activities did not include any specific performance measurement and tracking related efforts, quality attributes were getting ignored for cost and schedule. Subsequently high appraisal, prevention and failure costs were occurring which contributed to increasing COQ for project. The COQ was touching 44% as shown in COQ graph in figure 5, which ideally must not be higher than 20%. To control this as a first step CMMI level 2 was introduced.

### 4.2. Level 2

CMMI level 2 maturity is about inculcating discipline in project execution. This level initiates the shift from individual dependence to leadership of a manager. For realizing level 2 KPAs a performance testing process was required. Multiple rounds of brainstorming sessions of the work group along with client managers were done to define the performance testing process.

#### **Performance Testing Process**

The Performance Testing Life Cycle (PTLC) process was defined based on a classic waterfall model to guide, monitor and control performance testing projects [5]. It consisted of multiple phases with detailed activities, entry/exit criteria, templates and guidelines to streamline requirements management, measurement and analysis tasks for performance testing. The PTLC process is described in figure 3.

Figure 3: Performance Testing Life Cycle (PTLC)

A project management plan was prepared by the project manager based on the performance testing process and group reviewed by the work group. A PTLC phase wide effort estimation model was prepared based on the experience of the manager as similar project data was initially not available. A detailed project execution schedule was prepared and tracked by the project manager. These steps enforced a shift in project management priorities. Emphasis on size increased as compared to level 1 resulting in usage of better estimation techniques, which led to better planning and tracking activities.

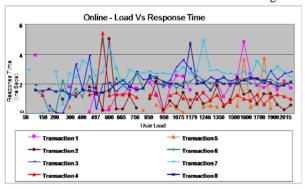

For ensuring performance tests quality and tracking met stated requirements, relevant performance metrics were monitored and reported from the system performance tests. Some of the metrics monitored were:

- 1. Utilization (CPU, Disk, Memory, Network)

- 2. Throughput

- 3. Response Time

- 4. User Load

For instance the reporting of response time versus user load graph helped in confirming the load level till which the SLA requirements were made. A sample graph of monitored response time versus the user load for various transactions from a COTS tool is shown below in figure 4.

Figure 4: Response Time vs User Load graph

The process helped to clearly define purpose, activities and outputs expected from COTs which made COTs selection more streamlined. Cost of COTs tailoring like parameters initialized, complexity of script writing, security/access requirements, were also factored in for their acquisition.

At this level along with test metrics, a process metrics culture was also inculcated. Metrics were defined to measure the operational goals, quality of deliverables and productivity of the team. Some of the metrics that excited upper management are listed below:

- Schedule Adherence

- Effort Variation

- Cost Of Quality

Quality check points were defined at the end of each project phase to monitor the project performance. Defect prevention activities based on the Pareto principle were started and their effectiveness was monitored by means of sub process goals such as:

- Defect Injection Rate in test data, scripts, scenarios etc.

- Review Effectiveness of test plans, scripts etc.

At this juncture there was visibility into the progress of achieving product and process goals as multiple metrics were captured. After one full cycle, some process capability baseline values were available for other projects in the client pipeline. For the next cycle of projects, goals were laid down based on this data. The quality and predictability were still not considered to be crucial for project success.

#### 4.3. Level 3

CMMI level 3 emphasizes on standardization of processes across the organization. To achieve it, the performance testing process and standards were institutionalized across client's testing teams. Training sessions were conducted to evangelize and enable people org wide with process implementation. This helped in effective adoption of processes by testing teams. In conjunction with different client project managers, working group established guidelines for the extent to which customization to the standard process were allowed for particular applications/projects.

Further emphasis on process engineering activities was drawn by making the related verification and validation activities an essential part of the process. The following verification activities were made mandatory: verifying test data for script parameterization, verification of test scenarios against the test strategy for evaluating the performance requirements correctly, checking that the load generated is as decided in the strategy, and the test report was reviewed for the monitored test results and graphs and so on. Compulsory validation activities included: validating the test environment by executing a sample test script using the load testing tool, executing the smoke tests for validating the test scripts etc. The performance test results were analyzed to find the performance gaps and suggest the best technical solutions. Based on cost, risks, effectiveness and time analysis, best solutions were agreed upon for implementation with development team. Knowledge sharing activities like preparation of a book of knowledge (BOK) were kick started for reuse.

At this level, meeting customer requirements of quality and speedy delivery took precedence over cost and size for the project manager.

#### 4.4. Level 4

At maturity level 4 the projects become more predictable as previous projects execution metrics provide a baseline and processes are in place to track them for adherence. In this case, use of standard reporting templates for capturing performance metrics during a few testing cycles provided an opportunity to provide performance's predictions in subsequent cycles. For doing so some additional performance engineering activities including scalability analysis, performance modeling and what-if analysis were conducted [6]. CPU utilization versus user load graph analysis was used to find if the application can scale up with the increasing user load. If an application is found to be scalable then its more predictable as throwing more hardware would allow it handle increase in load. Additionally performance models were created using test results and what-if analysis was done to predict the application performance for future user loads. SLA's were monitored and stored for future reference, which helped to individually predict the response time of the various applications under test and also to predict the response time for any new application for similar kinds of application tests in pipeline.

The project management focus was shifted to schedule and quality. From a process perspective, metrics data from individual quality check points defined at regular frequencies from various performance testing projects was used to build upon predictability. Using this data process capability baseline was established and referred for projects spanning across the organization.

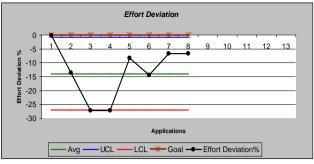

Statistical process control (SPC) techniques [7] were used to ensure that the process is within the control limits and variation is minimal at each quality check point. The SPC graph in figure 4 for effort deviation shows that effort deviation for initial applications/cycles was outside the control limit and later brought within the control limits. Tracking of this metric made effort deviation more predictable for next phases.

Figure 4: SPC for effort deviation

Process improvements were measured at every milestone. Analyzed optimization strategies were applied to performance testing projects across the organization. As a result costs were observed to be minimized across wide segments of the organization.

#### 4.5. Level 5

In this optimizing phase, innovation and defect prevention (DP) activities were continuously applied and improved. Some of the verifiable benefits seen include improved performance testing knowledge and skill level of the resources, which resulted in reduced time to market. The productivity and quality improvement strategies clearly lead to reduced cost of testing. There was more emphasis on quality and schedule with cost and size being given the back seat.

At this level there was focus on improving processes for dealing with business changes like technology changes, customer positioning, time to market, test execution methods etc. Decision analysis and resolution techniques were used to identify and implement new strategies. Process work flow was continuously updated and kept current. Implementation aspects of the key strategies and risk management planning were carried out as part of the detailed project plan.

Test management monitored and contributed towards improving following operational goals: COQ, productivity, quality, schedule adherence, effort variation and defect removal efficiency. These goals monitored at project level were mapped to organizational strategies due to which cross disciplinary cooperation and top management involvement in decision making became prominent.

At this level, the client realized the fact that "Prevention is always better than cure". So an upward trend was seen in prevention cost for quality, which automatically led to reduction in appraisal and failure costs. The end result was an overall reduction in cost of quality to 4%. Overall Cost of Quality [8] and its components observed at each level for a project are shown below.

Figure 5: COQ, appraisal, prevention and failure cost

The trend here shows that as the project matured usage of appropriate preventive measure like defect prevention, training and review activities brought down the failure cost where by improving the COQ.

#### 4. Benefits from CMMI implementation

Some of the important benefits achieved by CMMI guidelines implementation in this project were:

- Reduced testing cost Implementation and streamlining of performance testing processes helped increase productivity and reduced the failure cost. Thus an overall reduction in testing cost was achieved, which also increased profitability.

- Customer delight Addition of performance engineering activities helped reducing post production defects. Along with proper process this helped improved quality and reliability which made customers happy. This also improved repeat business.

- Reduced cycle time Continuous performance testing process improvements led to reduced cycle times for future releases. This positively impacted time to market, delivery time and increased bonuses for early delivery.

- Elevated employees' motivation Clarity of goals, activities to be performed and setup of tracking mechanisms increased employee morale and service provider's confidence. This decreased employee turnover and increased employee retention, reduced retraining costs and improved overall competitive advantage.

#### 5. Summary and Conclusion

In absence of processes, there is neither any guarantee of repeating the project success nor any basis for improving the productivity and/or quality. This paper summarized our experiences of using the CMMI framework for taking performance testing projects from initial ad-hoc executions to continuously optimizing levels. The benefits obtained at each maturity level in the presented case study accentuate the importance of model usage. So it is suggested to implement performance testing processes evolving using CMMI maturity model for delivering cost, schedule, size and quality effective projects and products.

#### 6. References

- [1] <u>http://en.wikipedia.org/wiki/Software\_performance\_t</u> <u>esting</u>

- [2] <u>http://www.sei.cmu.edu/cmmi/general/</u>

- [3] http://www.sei.cmu.edu/solutions/softwaredev/

- [4] "Capability Maturity Model® Integration (CMMISM), Version 1.1", CMMI Product Team, March 2002

- [5] J.D. Meier, Carlos Farre, Prashant Bansode, Scott Barber, "How To: Manage the Performance Test Cycle in a Regulated (CMMI) Environment", CodePlex website.

- [6] Pete Utton, Gino Martin, "Further Experiences with Software Performance Modelling", WOSP98, Santa Fe, NM.

- [7] <u>http://csqa.info/statistical process control spc</u>

- [8] <u>http://thequalityportal.com/q\_CoQ.htm</u>

# Not Your Father's or Grandfather's Mainframe Any More

David J. Lytle, Brocade Communications dlytle@brocade.com